引言:本文我们介绍下使用串行SPI Flash配置Xilinx 7系列FPGA的优点以及相应的配置方案实现细节,包括FPGA和SPI Flash之间的信号连接及如何选择恰当的SPI Flash。

1.简介

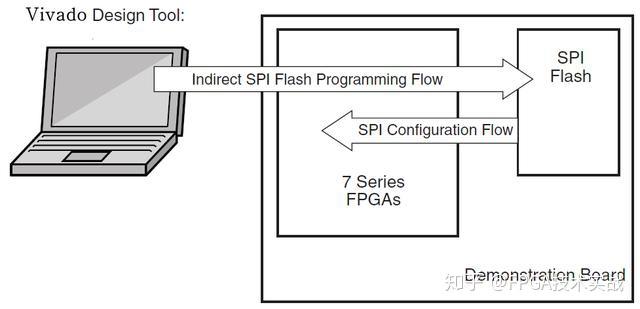

图1显示了利用Vivado开发工具间接编程SPI Flash和SPI Flash配置FPGA的示意图。

Xilinx FPGA由于其非易失特性,上电后需要一个配置比特流完成芯片内部逻辑配置。SPI Flash使用4线同步串行数据总线接口。SPI Flash只要求4个管脚来传输配置比特流,允许1bit或者2bit数据位宽。市面上较新的SPI Flash可选的支持6个管脚,4bit数据位宽,因此可以有效的降低配置时间。利用SPI Flash接口配置FPGA是一种非常低的引脚数配置解决方案,许多供应商都有各种密度的器件。

其他FPGA配置方案,如BPI接口NOR Flash,支持x8或者x16位宽配置方案,可以提供更快的配置速度,但是需要占用至少25个器件管脚。

由于并行NOR Flash设备比SPI Flash具有更高的密度选项,因此如果应用程序需要大量非易失性数据存储,或者需要存储多个FPGA位流,则应考虑BPI Flash。

2.SPI Flash基础

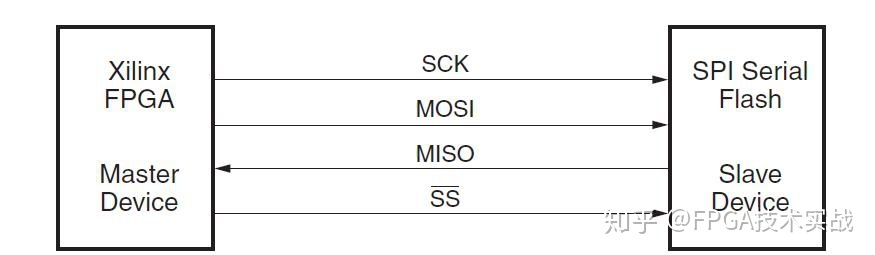

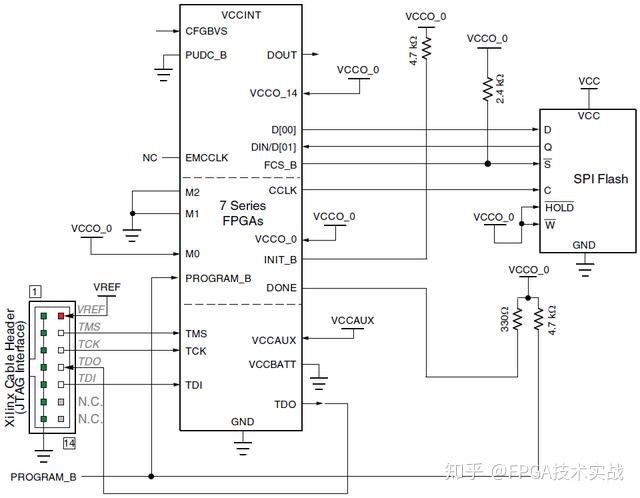

本小节我们回顾下SPI Flash的管脚功能和它们和7系列FPGA的硬件连接。图2显示了x1模式下基本的SPI Flash和FPGA之间的信号连接。

读命令和地址指令通过主输出从输入(MOSI)管脚从FPGA发送至SPI Flash,配置数据通过主输入从输出(MISO)管脚从SPI Flash返回至FPGA。SCK为同步时钟管脚,SS为低有效信号,为从器件片选信号。在x2数据位宽模式中,信号连接和图2相同,此时,MOSI管脚变为双向管脚,用作附加的数据管脚。

除了上述管脚之外,SPI Flash还有附加的管脚用于特殊用途。这些附加管脚随着SPI Flash供应商的不同而不同,但是有两个常见的功能管脚,保持(hold)和写保护(write protect)管脚。这两个特殊的管脚可选择作为附加的数据输出管脚,从而使SPI Flash数据位宽可以实现4bits,即x4模式。

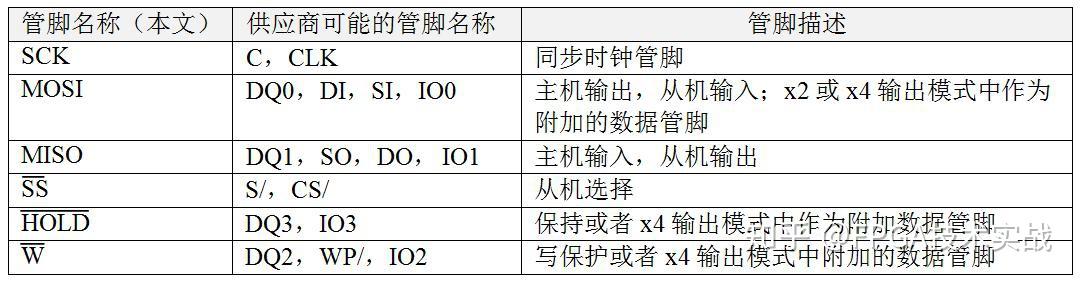

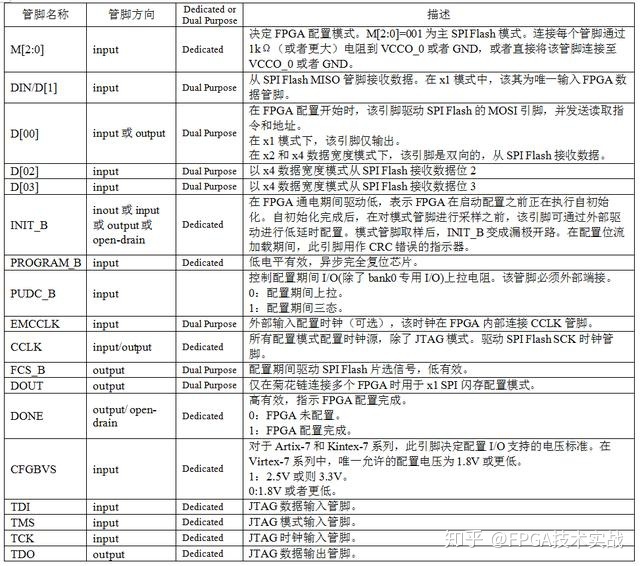

表1 SPI Flash管脚定义

2.1 SPI Flash选型

选择SPI闪存的第一个标准是密度。对于许多设计来说,这意味着选择一个足够大的flash设备来存储目标FPGA的配置比特流。对于某些设计,其他考虑因素缩小了使用闪存的选择范围,例如需要存储多个比特流,或者需要配置FPGA菊花链,或者配置速度。

1.器件密度:FPGA配置比特流的大小。UG470: 7 Series FPGAs Configuration User Guide 文档中给出了每种FPGA器件所需的配置比特流文件大小。如果设计需要多个比特流,则相应地乘以比特的大小。Xilinx工具允许比特流压缩,但是在确定SPI flash大小时不建议依赖压缩,因为压缩会随用户的设计而变化很大,而且是不可预测的。

2.配置时间:有些设计要求FPGA在指定的时间内完成配置。在这种情况下,设计者应考虑使用该闪存允许最快的读取时钟速率,并确保支持x4数据宽度的读取操作(有时在SPI flash数据表中称为x4输出为快速读取)。

3.I/O电压兼容性:设计者还必须考虑I/O电压兼容性。Aritx™-7和Kintex™-7系列支持高达3.3V的配置I/O电压,Virtex®-7系列支持高达1.8V的配置I/O电压。SPI Flash供应商通常为核心电压和I/O电压使用相同的电压源。但是,有些供应商可以使用单独的I/O电压引脚。

3.SPI Flash配置接口

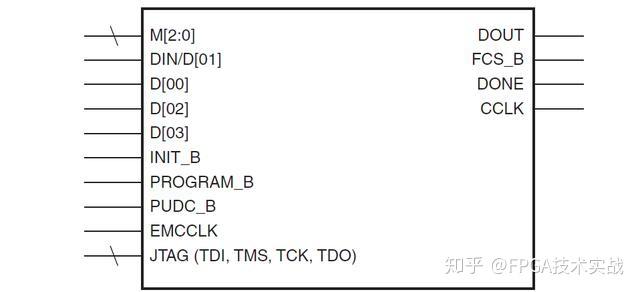

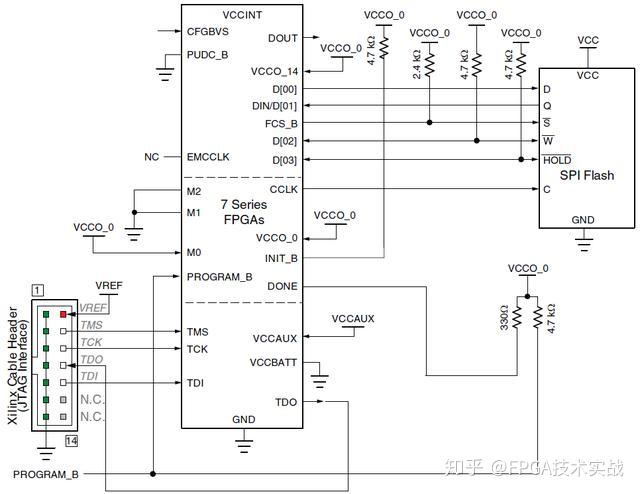

图3显示了SPI Flash配置要求的FPGA管脚。这些管脚中的许多管脚对于其他配置方案也是需要的,并不是SPI Flash专用的管脚。

表2详细说明了SPI Flash配置期间FPGA引脚的功能。除了SPI Flash基础部分中提到的管脚外,还显示了其他配置接口信号,这些信号提供了FPGA配置的状态信息和控制。

表2 SPI Flash配置管脚

图4和图5几乎相同。图4说明了x1或x2数据宽度模式下SPI Flash配置解决方案的连接。图5显示了x4数据宽度模式下SPI Flash配置解决方案的连接。图4和图5之间的唯一区别是如何处理HOLD和W引脚,它们在x1和x2数据宽度模式下上拉至VCCO_0,在x4数据宽度模式连接到7系列FPGA。

在图4SPI Flash x1/x2配置方案注意:

- DONE默认为开路输出,推荐连接外部上拉电阻;

- INIT_B是双向开路管脚,推荐外部上拉电阻;

- CCLK信号完整性非常管脚,需要当作高速信号处理;

- 从SPI Flash到FPGA的数据路径应考虑串联电阻,以尽量减少过冲。通过仿真可以确定合适的电阻值;

- FPGA配置I/O电压必须与SPI Flash I/O电压兼容;

- VCCBATT用于给SRAM供电,用于保存AES密钥。

在图5 SPI Flash x4配置方案注意:

- DONE默认为开路输出,推荐连接外部上拉电阻;

- INIT_B是双向开路管脚,推荐外部上拉电阻;

- CCLK信号完整性非常管脚,需要当作高速信号处理;

- 从SPI Flash到FPGA的数据路径应考虑串联电阻,以尽量减少过冲。通过仿真可以确定合适的电阻值;

- FPGA配置I/O电压必须与SPI Flash I/O电压兼容;

- VCCBATT用于给SRAM供电,用于保存AES密钥。

3.1 SPI Flash上电考虑

上电时,FPGA和SPI Flash之间存在竞争条件。FPGA完成自我初始化后,向SPI Flash发送读取命令,以检索配置数据,此时SPI Flash必须准备好,并对此作出响应命令。参考SPI Flash数据表中Flash完成自身初始化所需的时间。一般来说,7系列FPGA的自初始化时间(也称为上电复位)比SPI Flash(数百微秒)多一个数量级(毫秒),但设计者应评估时间。如果SPI Flash和FPGA位于不同的供电轨道上,这一点无疑更为重要。

3.2 SPI Flash配置FPGA

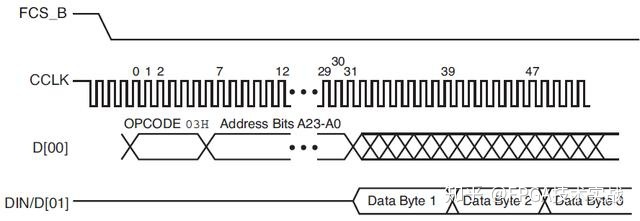

FPGA完成自初始化后,INIT管脚被释放,FPGA对模式管脚(M[2:0])采样,以确定使用哪种配置模式。当模式管脚M[2:0]=001时,FPGA在CCLK管脚输出大约3MHz的时钟频率 。很快之后,FCS_B驱动低电平,接着是x1快速读取指令和地址的操作码出现在D[00]引脚上,如图6所示。

数据最初以x1模式从SPI Flash传输到FPGA。在数据流早起部分,命令切换到外部时钟、x2或x4总线宽度或其他选项的命令。在读取这些选项之后,FPGA进行中间配置调整。

默认行为是从CCLK下降沿的SPI flash输出数据,并由FPGA在CCLK上升沿捕获数据。通过启用SPI_FALL_edge BitGen选项,可以将默认行为更改为在下降沿捕获。

4.SPI Flash配置时间计算

公式1应用于确定SPI Flash可以安全运行并且仍然可靠地传送比特流的最大频率。SPI Flash在时钟下降沿传输数据。7系列FPGA的默认设置是在时钟上升沿捕获数据。为了使下面的等式成立,假设启用了使FPGA能够在下降沿上捕获数据的SPI flash配置选项(-g SPI_fall_dege:yes). 这允许利用整个时钟周期,因此可以达到更高的频率。

最大时钟频率:

在7系列FPGA中,内部振荡器(fMCCKTOL)的频率容差非常重要。如果最短配置时间很关键,建议设计者使用外部时钟(EMCCLK)。

在确定最佳配置速率后,设计者需要将总比特流大小除以配置速率来确定x1模式下的总配置时间。如果使用x2或x4数据宽度,则除以宽度。

4.1 配置时钟计算举例

本节演示确定SPI Flash解决方案的最大操作配置频率的步骤。

选择的SPI flash是N25Q128A13,目标是Kintex-7xc7k325t FPGA。

- 根据SPI flash数据表,SPI Flash clock to out有多个值,取决于VCC和输出引脚上的电容。根据N25Q128A13的数据表,这些值最快为5ns,慢至7ns。在这个例子中,取7ns表示SPI Flash在30pf或更小的负载下运行。

- 根据Kintex-7xc7k325t FPGA器件手册,FPGA的建立时间为3.0ns。

- 从CCLK到C管脚的走线传播延迟和任何数据管脚的最长传播延迟提供TTPD。在这个例子中,使用的经验法则是每英寸165 ps,从FPGA到SPI闪存的走线长度为6英寸。(为了获得更精确的结果,建议使用其他技术,如IBIS模拟法。)在165ps/inch下,12英寸的跟踪值给出2.0ns。

- 因此时钟频率为:1/(7ns+3.0ns+2.0ns)=83.3MHz。

- 设计者应考虑使用FPGA的内部振荡器,最接近83.3 MHz的值为66 MHz。但是,XC7K325T的频率容差(fMCCKTOL)为±50%(当前值请参考DS182,Kintex-7 FPGA数据表),因此该时钟频率可能为(66 MHz x 1.5)=99 MHz,这对于计算的最大值来说太快了。

- 下一个最快的配置速率是50MHz,其最大频率为(50MHz×1.5)=75MHz。该速率远低于计算的最大值,名义上在50MHz下工作,远低于所需的83.3MHz。

- Kintex-7xc7k325t FPGA的比特流大小为91548896 btis。因此,在50MHz时钟下,需要的配置时间为:91548896/50000000 = 1.83s。

假设一个80MHz的振荡器已经在板上为另一个应用或设备服务,因此可以将其作为FPGA配置的时钟。此时,91548896/80000000 = 1.144s,使用x4数据位宽模式时,配置时间为1.144/4 = 286ms。

4.2 外部主时钟(EMCCLK)考虑

当使用外部主时钟(EMCCLK)作为配置时钟源时,EMCCLK必须包含在用户的设计中。否则会导致FPGA无法完成启动。当使用内部振荡器进行FPGA配置时,不需要特殊的设计要求。

5.小结

本文我们对使用SPI Flash配置FPGA进行了详细的说明,包括SPI Flash与FPGA配置管脚的硬件设计,SPI Flash的选型以及配置时间计算等。对于自己项目设计,我们要根据实际需求,合理的选择对应的配置方案,以达到设计的最优化。

更多技术文章可欢迎关注“FPGA技术实战”公众号,持续更新原创!